-Signal generator

-Vcc

-Ground

-Ic 74LS112

-SPDT

-Led

Rangkaian menggunakan clock dari signal generator sebagai jantung dari rangkaian.

lalu dihubungkan dengan clock flip flop jk.Kelebihan JK Flipflop adalah tidak ada kondisi terlarang yang dimana berapapun inputnya asalkan ada clock maka akan terjadi output. lalu set pada power dan reset pada ground yang dihubungkan nanti dengan spdt. Prinsip kerja dari JK flip-flop master / slave adalah sebagai berikut. Pertama, flip-flop master terpicu-pinggiran-positif dan flip-flop slave terpicu-pinggiran-negatif. Oleh karenanya, flip-flop master memberikan tanggapan terhadap masukan-masukan J dan K nya sebelum flip-flop slave. Jika J=1 dan K=0, flip-flop master diset pada saat pinggiran pulsa clock positif diberikan. Keluaran Q yang tinggi dari flip-flop utama mendrive masukan J pada flip-flop slave, maka pada saat pinggian pulsa clock negatif diberikan, flip-flop slave diset, menyamai kerja flip-flop master. Jika J=0 dan K=1, flip-flop master direset pada saat pinggiran naik pulsa clock diberikan. Keluaran Q yang tinggi dari flip-flop master menuju ke masukan K pada flip-flop slave. Oleh karenanya, kedatangan pinggiran turun pulsa clock mendorong flip-flop slave untuk reset. Sekali lagi, flip-flop slave menyamai kerja flip-flop master. Jika masukan J dan K pada flip-flop master adalah tinggi, maka flip-flop ini toggle pada saat pinggiran pulsa clock positif diberikan sedang flip-flop slave toggle pada saat pinggiran pulsa clock negatif diberikan. Dengan demikian, apapun yang dilakukan oleh flip-flop master, akan dilakukan pula oleh flip-flop slave: jika flip-flop master diset, flip-flop slave diset; jika flip-flop master direset, flip-flop slave direset pula.

Nanti rangkaian akan berjalan secara asyncronus karena bekerja secara bergantian atau tidak serentak .

1. Analisa output percobaan berdasarkan ic yang digunakan?

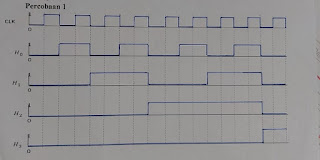

rangkaian ini adalah asyncronus diaman pencacah down counter

meenrapkan jk flip flop dimana output dari JK FLIP FLOP dimulai dari binner 1111,

1110, 1101, 1100, 1011, 1010, 1001, 1000, 0111, 0110, 0101, 0100, 0011, 0010,

0001, 0000 yang mana apabila dikonversi ke bilangan hexadesimal susunan bit-bit

ini akan menghasilkan output dari 15-0.Pada JK flip flop ke-2, input clock berasal dari output Q

komplemen pada JK flip flop yang pertama. Kemudian ouput dari JK flipflop

pertama membutuhkan 2 kali click untuk merubah outputnya.

2. Analisa sinyal output yang dikeluarkan jk flipflop kedua dan ketiga?

Pada Q komplemen JK

flipflop ke-2 akan berlogika 1, sehingga akan menjadikan inputan pada JK

flipflop ke-3 berlogika 1. lalu didapat dapatkan input berlogika 1, JK flipflop

ke-3 akan mengeluarkan output berlogika 1 pula.

Tidak ada komentar:

Posting Komentar